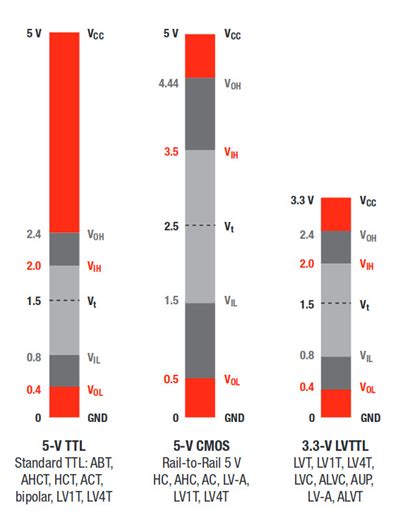

lvttl vs lvcmos The LV versions reffer to the supply and IO levels lower than the original 5V. LVTTL is 3.3V. LVCMOS too, but can be even lower (2.5V, 1.8V, .). An LVTTL can drive an original TTL because the output voltage specification of an LVTTL is within the TTL range. The . Manderville relic weapon. Guides. FFXIV guides. Endwalker Studium Delivery fish locations in FFXIV. Where to find and angle up the Studium Delivery fish. By Julia Lee @hardykiwis Dec 10,.58 Eschiva Thin Air: Trials of the Padjals: 58 Eschiva: Hands of Healing: 60 Raya-O-Senna Tetragrammaton Seeing White II

0 · lvttl33 lvcmos33

1 · lvttl vs lvcmos33

2 · lvttl vs lvcmos difference

3 · lvttl meaning

4 · lvpecl vs lvcmos

5 · lvcmos18 vs lvcmos33

6 · lvcmos vs cmos

7 · 3.3v ttl logic levels

One thing that is always in demand, is level 70 main hand weapons. This is particularly true for your fellow Gathering and Crafting classes. Just like yourself, everyone else is hitting.

The LV versions reffer to the supply and IO levels lower than the original 5V. LVTTL is 3.3V. LVCMOS too, but can be even lower (2.5V, 1.8V, .). An LVTTL can drive an original TTL because the output voltage specification of an LVTTL is within the TTL range. The .The low common-mode voltage (the average of the voltages on the two wires) of about 1.25 V allows LVDS to be used with a wide range of integrated circuits with power supply voltages d. Learn the differences and advantages of LVCMOS, LVTTL and LVDS, three types of digital signaling systems. See graphs, definitions and examples of voltage levels, noise .However, most CMOS logic circuits in use today are compatible with TTL and LVTTL levels which are the dominant 5 V and 3.3 V operating standards for DSPs. Note that 5 V TTL and 3.3 V .

LVTTL or LVTTL to GTL–/GTL/GTL+ translator • The LVTTL input are tolerant up to 5 .5 V allowing direct access to TTL or 5V CMOS • The GTL input/output operate up to 3 .6 V, .CMOS, HCMOS and LVCMOS CMOS is an acronym for Complementary Metal Oxide Semiconductor, which means that the Device (buffer) has been constructed of both p-channel .

Texas Instruments split-rail devices have two separate voltage supplies, one at each port. These devices allow for translation between 3.3-V LVTTL/LVCMOS to 5-V CMOS, 2.5-V CMOS to 5 .Introduction. As the world leader in logic, Texas Instruments (TI) offers a full spectrum of logic functions and technologies that range from the mature bipolar and bipolar complementary .

fake celine bags turkey

LVCMOS has the common CMOS input logic thresholds of ⅓ and ⅔ the rails, whereas LVTTL still retains the 0.8 V and 2.4 V thresholds. So for FPGAs: the difference between LVTTL and .Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3V applications. It uses an LVTTL input buffer and push-pull output buffer.Low voltage complementary metal oxide semiconductor (LVCMOS) is a low voltage class of CMOS technology digital integrated circuits. Overview. To obtain better performance and .Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3V applications. It uses an LVTTL input buffer and push-pull output buffer. Table 2-35. Minimum and .

The MAX9160 125MHz, 14-port LVTTL/LVCMOS clock driver repeats the selected LVDS or LVTTL/LVCMOS input on two output banks. Each bank consists of seven LVTTL/LVCMOS series terminated outputs and a bank enable. The LVDS input has a fail-safe function. The MAX9160 has a propagation delay that can be adjustedSCEA035A Selecting the Right Level-Translation Solution 5 0 3 1 2 0 2030 40 5060 8010 70 1.8 V Input 3.3 V Output Voltage − V Time − ns 0 3 1 2 02030405060 8010 70CMOS Voltage vs. Speed Table of Contents Logic Guide 2017 2oduction and Contents Intr Logic Overview 3orld of TI Logic W 4 IC Basics 5 Automotive Logic . 3.3-V LVTTL LVT, LV1T, LV4T, LVC, ALVC, AUP, LV-A, ALVT 5 VV CC 4.44 VOH 3.5 VIH 3.3 VV CC 1.5 Vt 2.4VOH 0.8 V IL 2.0 VIH 0.4 VOL O.5V OL 1.5V IL 2.5 Vt 0 GND 0 GND 0 GND 0 GND 0.45VOL 1.17 VIH Re: FPGA LVCMOS vs LVTTL standards « Reply #1 on: August 29, 2021, 11:34:19 am » LVTTL has the same input thresholds as TTL and they match 3.3 volt CMOS pretty well so they may be using the same receiver for both.

Low voltage complementary metal oxide semiconductor (LVCMOS) is a low voltage class of CMOS technology digital integrated circuits. Overview. To obtain better performance and lower costs, semiconductor manufacturers reduce the device geometries of integrated circuits. With each reduction the associated operating voltage must also be reduced in .

For example, a Xilinx spartan-6 IOB (see table 1-5 in this) will happily support inputs that use e.g. LVTTL, LVCMOS33, and LVCMOS18 on a bank with a 2.5V VCCIO and without an additional reference voltage, as long as the configuration properly indicates the correct bank voltage for each bank and the correct signalling standard for each pin.

LVCMOS has the common CMOS input logic thresholds of ⅓ and ⅔ the rails, whereas LVTTL still retains the 0.8 V and 2.4 V thresholds. So for FPGAs: the difference between LVTTL and LVCMOS is simply the input logic thresholds. The outputs swing to the I/O bank supply. At this voltage I can select drive strengths 2mA for LVCMOS and 8mA for LVTTL. If I reduce the voltage to 3.0V, I can select drive strength 16mA for both LVCMOS and LVTTL. I have been able to translate the IBIS models to spice. Results: - CMOS is faster than LVTTL at the same voltage(3.0V) + drive strength (16mA).the Voh for your LVCMOS or LVTTL standard both at light load, where it should be . very near the power rail, and at the rated current for the standard where it just. needs to meet the Vih of the standard plus some margin. If your outputs are driving. into a low impedance load you could also get the voltages you are seeing. Regards, GaborSLLA120 6 Interfacing Between LVPECL, VML, CML, and LVDS Levels 3.1.2 Input Stage for Devices Using LVPECL Drivers The TNETE2201 input stage consists of a differential pair which requires its inputs (Input+ and

standards, such as 1.8 V, 1.5 V, or 1.2 V LVTTL or LVCMOS, 3.0 V PCI or PCI-X , voltage-referenced, and differential I/O standards, do not require attention on the maximum input voltage. Interfacing Intel ® FPGA Devices with 3.3/3.0/2.5 V LVTTL/LVCMOS I/O Systems 683295 | 2022.03.28 AN 447: Interfacing Intel ® FPGA Devices with 3.3/3.0/2.5 V .

- 3 input pins TTL 5V -> LVTTL/LVCMOS 3.3V - 3 I/O pins TTL 5V <-> LVTTL/LVCMOS 3.3V. Basically, I need a bidirectional level voltage translator (at least for the three I/O pins) that can convert TTL5V into LVTTL/LVCMOS so I don't overpower the input pins of my Kintex 7 board. I can't find a solution to do that. Have you got any suggestions ?ttl电平 vcc:5v数字电路中,由ttl电子元器件组成电路使用的电平。电平是个电压范围。 标准输出高电平(voh):2.4v 标准输出低电平(vol):0.4v(0.5v) 通常输出高电平:3.5v(3.6v) 通常输出低电平:0.2v 最小输入.levels that accept 1 .8-V LVCMOS signals, while operating from either a single 3 .3-V or 2 .5-V VCC supply . The SN74AUP1Txx with configurable logic function (‘57,’58,’97,’98) can be easily . LVTTL or LVTTL to GTL–/GTL/GTL+ translator • The LVTTL input are tolerant up to 5 .5 V allowing direct access to TTL or 5V CMOS

LVCMOS/LVTTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock frequency of 85 MHz, 24 bits of

Corresponding to 3.3V LVTTL, LVCMOS appeared, which can directly drive each other with 3.3V LVTTL. 3.3V LVCMOS: Vcc: 3.3V; VOH>=3.2V; VOL<=0.1V; VIH>=2.0V; VIL<=0.7V. (VIH refers to the voltage value at which the input gate is high level, and VIL refers to the voltage value at which the output gate is low level)Corresponding to 3.3V LVTTL, LVCMOS appears, which can directly drive each other with 3.3V LVTTL. 3.3V LVCMOS: Vcc: 3.3V; VOH>=3.2V; VOL<=0.1V; VIH>=2.0V; VIL<=0.7V. 2.5V LVCMOS: Vcc: 2.5V; VOH>=2V; VOL<=0.1V; VIH>=1.7V; VIL<=0.7V. CMOS use note: There is a thyristor structure in the CMOS structure. When the input or input pin is higher than a .

SN65EPT22 3.3 V Dual LVTTL/LVCMOS to Differential LVPECL Buffer 1 Features 3 Description The SN65EPT22 is a low power dual LVTTL to 1• Dual 3.3V LVTTL to LVPECL Buffer LVPECL translator device. The device includes • Operating Range circuitry to maintain known logic HIGH level when – LVPECL VCC = 3.0 V to 3.6 V With inputs are in open .Corresponding to 3.3V LVTTL, LVCMOS appears, which can directly drive each other with 3.3V LVTTL. 3.3V LVCMOS: Vcc: 3.3V; VOH>=3.2V; VOL<=0.1V; VIH>=2.0V; VIL<=0.7V. 2.5V LVCMOS: Vcc: 2.5V; VOH>=2V; VOL<=0.1V; VIH>=1.7V; VIL<=0.7V. CMOS use note: There is a thyristor structure inside the CMOS structure. When the input or input pin is higher ."3.3-v lvcmos", "3.3v lvcmos", "lvcmos" 3.3-V LVTTL All Intel device families supported by the Quartus ® Prime software

图5、lvcmos i/o可用的bank类型. 7系列fpga支持的lvcmos标准:lvcmos12、lvcoms15、lvcmos18、lvcmos25和lvcmos33。这几种lvcmos i/o标准支持的输出驱动电流存在差异。单向和双向lvcoms端接方式和lvttl类似。图6和图7分别举例单向和双向lvcoms端接方式。

LVTTL/LVCMOS Translator MC100EPT21 The MC100EPT21 is a Differential LVPECL/LVDS/CML to LVTTL/LVCMOS translator. Because LVPECL (Positive ECL), LVDS, and positive CML input levels and LVTTL/LVCMOS output levels are used, only +3.3 V and ground are required. The small outline 8−lead SOIC package makes the EPT21 ideal for applications

3 3. -V LVTTL 1 8. V V C C 1. 3 5V V OH 0. 6 3V V IL 1. 1 7V V IH 0 4 V . V OL 0 9. V V t 0 V GN D 18. -V C MOS Figure 1. Logic Thresholds If a processor on a 1.8-V voltage rail is controlling a signal switch with a supply rail of 3.3 V without integrated 1.8-V logic capability, the system is required to use an external translator as shown

I want to provide a single-ended signal from an Intel Cyclone 10 GX FPGA to SN75LVDS387 and the signal is 2.5 LVCMOS rather than LVTTL. The FPGA does also output 3.0 LVTTL, but the available pins are much less and do not meet our requirements. The SN75LVDS387 datasheet does not seem to explicitly list LVCMOS input support, but hints it. As you move to the right, you'll see the top of the chart is 3.3V. 2.5V Logic, such as Microchip's published minimum operating voltage on some microcontrollers, is a difficult voltage to interface with externally, as 2.5v is considered High or indeterminate value on 3.3V logic, and low or indeterminate on 5V CMOS.translation between 3.3-V LVTTL/LVCMOS to 5-V CMOS, 2.5-V CMOS to 5-V CMOS, 2.5-V CMOS to 3.3-V LVTTL/LVCMOS, and vice versa. Device Description Dual-Supply Bus Transceivers The SN74LVC4245A (see Figure 3) is an 8-bit (octal) noninverting bus transceiver that has two power-supply rails. The A port is set at 5 V, while the B port is set at 3.3 V.

lvttl33 lvcmos33

In order to unlock FFXIV The Twinning, much like the other level 80 dungeons introduced in the Shadowbringers expansion, you first have to have beaten the main story quest. Make sure you.

lvttl vs lvcmos|3.3v ttl logic levels